雷达中频数据采集

一、系统概述

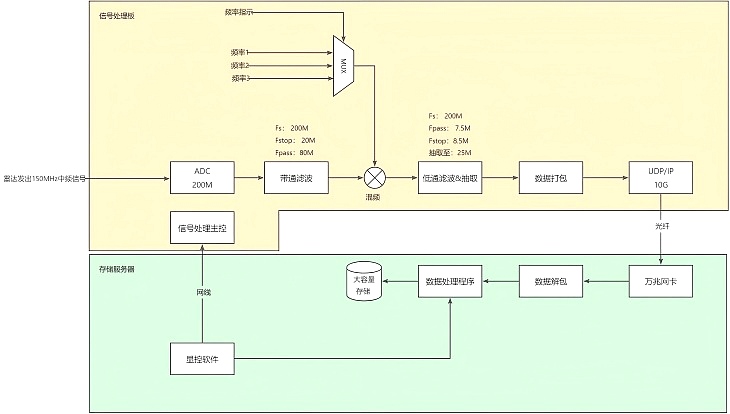

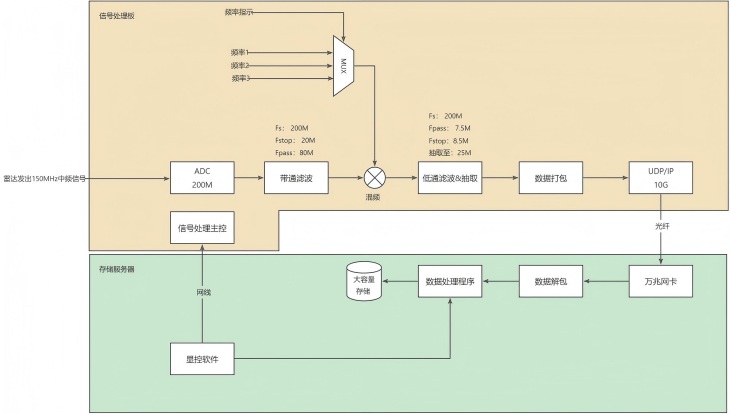

本系统的目标是实现雷达中频信号的高速采集、实时处理与可靠存储。雷达在运行过程中,会产生大量中频信号数据,这些数据既是后续信号处理的基础,也是任务复盘与性能分析的重要依据。为了保证数据的完整性与可追溯性,本方案采用了前端信号处理板与后端存储服务器相结合的架构,利用高速模数转换器、可编程逻辑器件和万兆网络,实现从采集到落盘的全链路闭环。

整体方案由两部分构成:一是基于 FPGA的信号处理板,负责数据的采集、数字变换与网络打包;二是基于高性能 PC 的存储服务器,内置磁盘阵列,负责数据接收、存储和用户交互。该系统既满足高采样率和大数据吞吐的需求,又提供直观的操作界面,使技术人员与使用人员能够高效完成数据获取和管理任务。

二、信号处理板设计

信号处理板的核心器件包括高速模数转换器(采样率 250 MS/s)和 FPGA。当雷达发射机产生 150 MHz 中频信号后,首先由 ADC 进行采样,并将信号转化为数字序列输入 FPGA。FPGA 内部完成一系列数字信号处理操作,包括带通滤波、下变频、低通滤波及抽取等步骤,从而将中频信号转化为适合存储和分析的基带或低频信号。

经过处理后的数据被组织为固定格式的 UDP 报文,并通过 10G 光纤链路实时传输到存储服务器。在报文生成过程中,FPGA 不仅负责将 IQ 数据按块打包,还会插入任务标识、时间戳和方位码等信息,确保后端能够精确地还原采集时的信号状态。这种处理方式既保证了数据的时序完整性,又为后期分析提供了丰富的元数据。

采集存储原理框图

三、UDP 报文结构

信号处理板与存储服务器间采用 UDP/IP 协议进行高速传输。每个 UDP 报文由报头和 IQ 数据两部分组成,报头固定长度为 16 字节,包含关键信息字段。报文格式如下表所示:

标识 | ||

采样率 | ||

时间戳 | ||

包序号 | ||

方位码 | ||

预留 | ||

IQ 数据 |

四、存储服务器设计

存储服务器由高性能 PC 及其配套的磁盘阵列组成。服务器通过万兆网卡接收来自 FPGA 的 UDP 数据流,并对数据进行实时解包和校验。解包后的 IQ 数据按照任务编号和时间索引存储在磁盘阵列中,采用分段存储方式,每个文件对应固定时长的数据段,既便于管理,也方便后续调用和分析。

五、用户操作与界面

为了方便用户使用,本系统提供了直观的操作界面,涵盖数据管理、波形展示和参数设置三个方面。

在数据管理方面,用户可以对存储的数据进行增加、删除和查询操作,文件按照时间段和任务编号组织,检索效率高,操作简便。在波形展示方面,界面能够实时显示 IQ 数据的时域波形,并可进行频域变换,生成频谱图,帮助使用人员直观判断信号质量与干扰情况。同时,系统还支持数据回放功能,用户可以选择历史数据段,重现当时的采集场景。

在参数设置方面,界面提供了采样率、抽取比、滤波带宽以及方位码等参数的配置功能,用户可以根据任务需求灵活调整采集条件。所有操作均通过图形化界面完成,既适合专业人员进行精细配置,也便于非专业人员快速上手。

六、系统特点与应用价值

本系统在设计中充分考虑了雷达中频采集的高速性、连续性和可靠性。通过 FPGA 的实时处理能力和 10G 光纤的高速链路,保证了数据采集的完整性;通过合理的报文格式和磁盘阵列架构,确保了数据存储的可追溯性和长期有效性;通过友好的用户界面和管理功能,提升了系统的易用性和操作效率。

在应用层面,该系统不仅可用于日常任务的中频采集与存档,还可支持科研实验、算法验证以及战术应用。数据的可回放与频谱分析功能,为雷达系统的性能优化和干扰环境评估提供了有力支撑。